# M16C/26

# Using the A-D Converter in Single Shot Mode

## 1.0 Abstract

The following document outlines the steps necessary to setup, perform and read a single conversion using the onboard analog to digital converter (ADC) of the M16C/26. The ADC is useful in measuring output voltages of sensors such as accelerometers or other analog instrumentation and converting them to digital values.

#### 2.0 Introduction

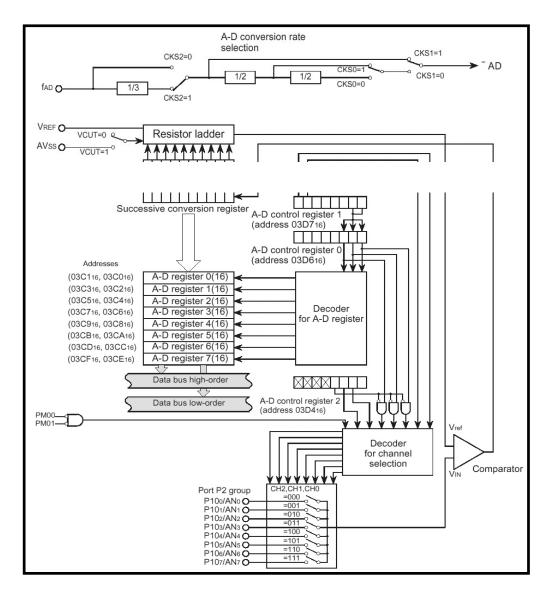

The Renesas M30262 is a 16-bit MCU based on the M16C/60 series CPU core. The MCU features include up to 64K bytes of Flash ROM, 2K bytes of RAM, and 4K bytes of Virtual EEPROM. The peripheral set includes 10-bit A/D, UARTS, Timers, DMA, and GPIO. The M16C/26 features an onboard analog to digital converter (ADC). The ADC consists of one 10-bit successive approximation circuit with a capacitive coupled amplifier. There are eight analog input pins, selectable conversion clock speeds, sample and hold function, and several conversion modes. Table 1 shows the performance of the ADC and Figure 1 shows a diagram of the ADC block.

| Item                            | Performance                                                                                                                                                                                                             |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Method of A-D Conversion        | Successive approximation (capacitive coupling amplifier)                                                                                                                                                                |  |  |  |

| Analog input voltage            | 0V to AVcc (Vcc)                                                                                                                                                                                                        |  |  |  |

| Operating clock f <sub>AD</sub> | $f_{AD}, f_{AD}2, f_{AD}3, f_{AD}4, f_{AD}6$ , or $f_{AD}6$ or $f_{AD}12$ where $f_{AD}=f(Xin)$                                                                                                                         |  |  |  |

| Resolution                      | 8-bit or 10-bit (selectable)                                                                                                                                                                                            |  |  |  |

| Operating modes                 | One-shot mode, repeat, single sweep mode, repeat mode, repeat sweep mode 0 and repeat sweep mode 1.                                                                                                                     |  |  |  |

| Analog input pins               | 8 pins AN <sub>0</sub> to AN <sub>7</sub>                                                                                                                                                                               |  |  |  |

| A-D conversion start condition  | Software trigger: A-D conversion starts when the A-D conversion start flag changes to "1"                                                                                                                               |  |  |  |

|                                 | External trigger (can be retriggered): A-D conversion starts when the A-D conversion start flag is "1" and the $AD_{TRG}$ /P15 input (shared with INT3) changes from "H" to "L"                                         |  |  |  |

| Conversion speed per pin        | Without sample and hold function 8-bit resolution: 49 $f_{AD}$ cycles, 10-bit resolution: 59 $f_{AD}$ cycles. With sample and hold function 8-bit resolution: 28 $f_{AD}$ cycles, 10-bit resolution:33 $f_{AD}$ cycles. |  |  |  |

#### Table 1 ADC Performance

#### Figure 1 ADC Block Diagram

# 3.0 One-Shot Mode Description

In one shot-mode, one pin of the ADC is selected as the input source. Once triggered, a conversion takes place on the selected pin and the result is stored in the ADC result register corresponding to the selected channel. An interrupt signifies the completion of a conversion. An overview of the registers that will be used in this example is shown below. These registers are detailed in the included sample code. For specific details, consult the MCU specification for the device in question. Figure 2 and Figure 3 show the control registers for the ADC in One-Shot Mode.

| A-D control register 0                | ) (Note 1)                    |                                    |                                                                                             |          |

|---------------------------------------|-------------------------------|------------------------------------|---------------------------------------------------------------------------------------------|----------|

| b7 b6 b5 b4 b3 b2 b1 b0               | Symbol<br>ADCON               |                                    | When reset<br>00000XXX2                                                                     |          |

|                                       | Bit symbol                    | Bit name                           | Function                                                                                    | RW       |

|                                       | CH0                           | Analog input pin select<br>bit     | 0 0 0 : AN0 is selected<br>0 0 1 : AN1 is selected                                          | 00       |

|                                       | CH1                           |                                    | 0 1 0 : AN2 is selected<br>0 1 1 : AN3 is selected<br>1 0 0 : AN4 is selected               | 00       |

|                                       | CH2                           |                                    | 1 0 1 : AN5 is selected<br>1 1 0 : AN6 is selected<br>1 1 1 : AN7 is selected (Note 2)      | 00       |

|                                       | MD0                           | A-D operation mode                 | 0 0 : One-shot mode (Note 2)                                                                | 00       |

| · · · · · · · · · · · · · · · · · · · | MD1                           | select bit 0                       | · · · · · · · · · · · · · · · · · · ·                                                       | 00       |

| L                                     | TRG                           | Trigger select bit                 | 0 : Software trigger<br>1 : ADTRG trigger                                                   | 00       |

|                                       | ADST                          | A-D conversion start flag          | 0 : A-D conversion disabled<br>1 : A-D conversion started                                   | oю       |

|                                       | CKS0                          | Frequency select bit 0             | Refer to table 1.18.2                                                                       | 00       |

|                                       | I (Note 1)<br>Symbol<br>ADCON |                                    | When reset<br>0016                                                                          |          |

|                                       | Bit symbol                    | Bit name                           | Function                                                                                    | RW       |

|                                       | SCAN0                         | A-D sweep pin<br>select bit        | Invalid in one-shot mode                                                                    | 00       |

|                                       | SCAN1                         |                                    |                                                                                             | 00       |

|                                       | MD2                           | A-D operation mode<br>select bit 1 | Set to 0 when this mode is selected                                                         | 00       |

|                                       | BITS                          | 8/10-bit mode select bit           | 0 : 8-bit mode<br>1 : 10-bit mode                                                           | oо       |

|                                       | CKS1                          | Frequency select bit1              | Refer to table 1.18.2                                                                       | 00       |

| L                                     | VCUT                          | Vref connect bit (Note 2)          | 1 : Vref connected                                                                          | 00       |

| L                                     | Nothing is<br>In an atten     |                                    | rite 0. The value, if read, turns out to be 0.                                              | 00       |

|                                       |                               |                                    | n, the conversion result is indeterminate.<br>√ref connected), wait for 1 μs or more before | starting |

# Figure 2 ADC Control Registers in One-Shot Mode

| A-D control register 2 (Note 1)                                                                         |                                   |                                                                                  |                                                         |        |  |  |  |

|---------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------|--------|--|--|--|

|                                                                                                         | Symbol<br>ADCON2                  |                                                                                  | When reset<br>0016                                      |        |  |  |  |

|                                                                                                         | Bit symbol                        | Bit name                                                                         | Function                                                | RW     |  |  |  |

|                                                                                                         | SMP                               | A-D conversion method<br>select bit                                              | 0 : Without sample and hold<br>1 : With sample and hold | 00     |  |  |  |

|                                                                                                         | Reserved bits                     |                                                                                  | Must always be set to 0                                 | 00     |  |  |  |

|                                                                                                         | CKS2                              | Frequency select bit 2                                                           | Refer to table 1.18.2                                   | 00     |  |  |  |

| L.I.I.                                                                                                  | Nothing is ass<br>In an attempt t |                                                                                  | 0. The value, if read, turns out to be 0.               |        |  |  |  |

|                                                                                                         |                                   | -D control register is rewritte                                                  | en during A-D conversion, the conversion                | result |  |  |  |

| A-D register i Symbol Address When reset<br>ADi(i=0 to 7) 03C016 to 03CF16 Indeterminate<br>b7 b0 b7 b0 |                                   |                                                                                  |                                                         |        |  |  |  |

|                                                                                                         |                                   |                                                                                  | Function                                                | RW     |  |  |  |

|                                                                                                         | L.                                | Eight low-order bits of A-D                                                      | conversion result                                       | ∣ ×    |  |  |  |

|                                                                                                         |                                   | During 10-bit mode<br>Two high-order bits of                                     | A-D conversion result                                   | o x    |  |  |  |

|                                                                                                         |                                   | During 8-bit mode<br>When read, the conter                                       | nt is indeterminate                                     | ××     |  |  |  |

|                                                                                                         |                                   | Nothing is assigned.<br>In an attempt to write to th<br>read, turns out to be 0. | ese bits, write 0. The value, if                        |        |  |  |  |

Figure 3 ADC Control Registers

# 4.0 Example Program

The following example program demonstrates how to perform a conversion using the ADC with the following configuration.

- Single shot conversion

- 10-bit mode

- Analog input 0 used

- Sample and hold enabled

- Internal Vref

- Conversion clock used will be f<sub>AD</sub> /4 (When f(Xin) is greater than 10 MHz, f<sub>AD</sub> must be divided)

- · Software conversion start

### 5.0 Reference

#### **Renesas Technology Corporation Semiconductor Home Page**

http://www.renesas.com

#### E-mail Support

support\_apl@renesas.com

#### Data Sheets

• M16C/26 datasheets, M30262eds.pdf

#### User's Manual

- M16C/20/60 C Language Programming Manual, 6020c.pdf

- M16C/20/60 Software Manual, 6020software.pdf

- MSV30262-SKP or MSV-Mini26-SKP Quick start guide

- MSV30262-SKP or MSV-Mini26-SKP Users Manual

- MDECE30262 or MSV-Mini26-SKP Schematic

### 6.0 Software Code

The sample software provided was written in C and compiled using the KNC30 compiler. The program performs one conversion on reset. This code could be simply modified to use a timer for the trigger of the ADC to provide multiple conversions at specific intervals. The example program was written to run on the MSV30262 Starter Kit but could be modified to implement in a user application.

```

DESCRIPTION: single shot.c

PURPOSE: Outlines how to use the M16C/262 ADC in single shot mode.

*

On reset, program stores the result of the conversion in a variable that

can be examined using

KD30 or similar tool.

#include "sfr26.h"

int TempStore = 0x0000; // Location where ADC result is stored

#pragma INTERRUPT ADCInt // Compiler directive telling where

// the ADC interrupt is located

void ADCInt(void);

/*

** main

* PARAMETERS: None

* DESCRIPTION: Main function. Where program execution starts. Sets

up the ADC then waits for interrupt to occur.

* RETURNS: Nothing

*/

void main (void) {

|||||||_____Analog input select bit 1

|||||| _____Analog input select bit 2

|||||_____A/D operation mode select bit 0

A/D operation mode select bit 1

Trigger select bit

A/D conversion start flag

Frequency select bit 0*/

adcon1 = 0x38;

/*

00101000; /* 10-bit mode, fAD/4, Vref connected

|||||||

A/D sweep pin select bit 0

||||||

A/D sweep pin select bit 1

||||||

A/D operation mode select bit 1

|||||_____8/10-bit mode select bit

||||_____Frequency select bit 1

_____Vref connect bit

Reserved

Reserved */

```

# RENESAS

In order for this program to run properly, ADC interrupt vector needs to point to the interrupt function, ADCInt. The ADC interrupt vector in "sect30.inc" must be modified as shown below.

File Name: sect30.inc ; Content: Section include file for MSV30262-SKP. ; Copyright 2003 Renesas Technology America, Inc. ; All rights reserved ; \$Log:\$ ; : : .lword dummy\_int ; DMA1(for user)(vector 12) .lword dummy\_int ; Key input interrupt(for user)(vect 14) .glb \_ADCInt .lword ADCInt; A-D(for user) (vector 14).lword dummy\_int; uart2 transmit(for user) (vector 15).lword dummy\_int; uart2 receive(for user) (vector 16) : :

### Keep safety first in your circuit designs!

Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

# Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corporation or a third party.

- Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

• Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.